# DESIGN OF A DIGITAL MULTI-CHANNEL ANALYZER BASED ON FPGA FOR HPGe DETECTOR

### HOANG MINH VU, NGUYEN VAN KIEN, PHAM NGOC SON, PHAM HOAI PHUONG, NGUYEN XUAN TAN

Nuclear Research Institute, Dalat city, Vietnam <u>hminhvu@gmail.com</u>

**Abstract:** This study presents a design of digital multi-channel analyzer (DMCA) based on Field-programmable gate array (FPGA) for HPGe detector. The main hardware of DMCA is implemented by using a 16-bit ADC with 105 Msps and Artix-7 FPGA. The algorithms of pulse shaping filter, detecting peaks and spectrum histogram processing are designed and simulated by using MATLAB. Therefore, the FPGA resources are optimized, leading to cost-effective hardware. Due to all algorithms implemented on FPGA, the DMCA performs in real-time. The pileup problem and baseline restoration are carefully processed to improve the energy resolution. The DMCA was examined with an HPGe detector of GC1518 model of Canberra with <sup>137</sup>Cs, <sup>60</sup>Co and <sup>133</sup>Ba sources. The energy resolution of the DMCA at 1332 keV <sup>60</sup>Co has attained 3.1 keV. With this result, the prototype system of the DMCA is highly promising for a multi-DMCA system in considering performance, cost and size.

## Keywords: DMCA, FPGA, HPGe

## **I. INTRODUCTION**

The pulse spectroscopy systems are widely applied in many areas such as in nuclear physics research, in industrial and medical applications. Due to their important roles, they have been developed since the early 1950s [1]. Pulse processing is a main objective in the pulse spectroscopy to minimize distortion and electronic noise, and to increase performance and accuracy. A system for traditional analogical signal processing, which consists of a preamplifier, amplifier, analog pulse shaping, and digital-to-analog converter, has a large pileup probability and dead time, and complicated connection [7, 5]. With growing demands for high performance, low cost and small size of DMCA systems in nuclear data acquisition, the digital signal processing (DSP) is a new approach in designing of a radiation spectroscopy system. Recently, many advanced techniques of digital pulse processing to improve DMCA have been reported in [2, 3, 4, 5, 6, 7, 8, 9]. A real-time digital trapezoidal pulse shaping was employed to increase throughput and maintain the energy resolution [6]. However, the throughput is still restricted at a high input count rate and a hardware used is expensive. A costeffective and high performance digital signal system based on microcontroller for performing an advanced pulse processing algorithm was introduced but the input count rate is still under 61 kcps [7]. A complicated pulse shaping filter named Mexican Hat Wavelet configured on FPGA was proposed for improvement of the energy resolution and the peak-Compton ratio [8]. However, consumption of FPGA logic resources and quality of spectrum at low energy regions are still debatable to apply in low cost and high quality measurement systems.

Aiming at high performance and low cost, the DMCA was designed and implemented based on low cost FPGA. The combination of finite impulse response (FIR) and digital trapezoidal filter for shaping filter, peaks detection, pile-up rejection, baseline restoration, and spectral histogram processing are simulated and optimized by using Matlab to obtain energy resolution and minimize FPGA logic resources. Two main IC, i.e. XC7A35T (Xilinx FPGA Artix7) and AD6645 are chosen for DMCA hardware. The DMCA was tested with a HPGe detector GC1518 model of Canberra and using <sup>137</sup>Cs, <sup>60</sup>Co and <sup>133</sup>Ba standard sources.

## **II. PULSE PROCESSING SYSTEM DESIGN**

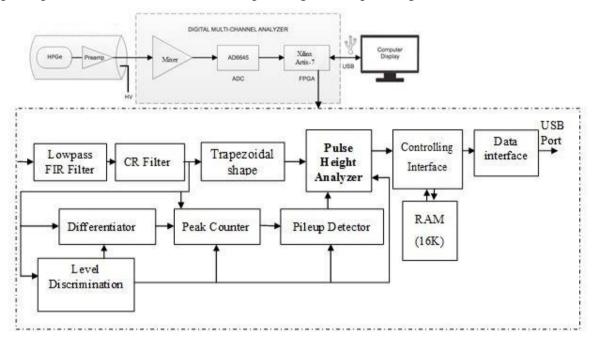

A complex algorithm can configure a fast and large resource FPGA to obtain high performance of the DMCA but the cost is high, especially for multi-DMCA systems [8, 5, 6]. To reduce the cost of system, this work adopts two main used IC, i.e. Artix-7 XC7A35T and AD6645. The AD6645 has 14-bit resolution, and a 105 Msps sample rate. The Artix-7 FPGA family provides low power consumption, high DSP, and logic throughput in a cost-optimized FPGA [13]. To be a simple circuit, only a clock rate of 50 MHz is exploited to synchronize the clock of ADC and FPGA. The block diagram of DMCA configured on FPGA is shown in Figure 1. To enhance signal to noise ratio (SNR), a mixer using op-amp (AD847) is inserted between preamplifier and ADC to transform unipolar signal to bipolar signal.

Fig.1. Schematic system of the DMCA.

The incoming signal from the preamplifier is constantly digitized by ADC and then the code of ADC is conveyed to FPGA. The pulse shaping filter, detecting peaks, spectrum histogram processing, controlling interface, and communication with computer (PC) are performed by FPGA.

The analysis algorithms such as pulse shaping filter, threshold discrimination, pileup treatment and pulse height analyzer of DMCA using raw data collecting from ADC are simulated by Matlab to inspect the performance of DMCA. A 40th-order FIR low pass filter using Hamming Window with a cutoff frequency of 1.5 Mhz as Ref. [10, 11] is employed to remove high-frequency harmonics of input signal from ADC. To increase the SNR, minimize the baseline drifts and reduce pileup, the CR filter approach is next processing to filter and shorten pulse [12]. After the pulse filter, the signal moves to a signal threshold discrimination to create logic pulse for controlling next function blocks such as differentiator, peak counter, pileup detector and pulse height analyzer. The differentiator is used to reveal peaks and detect pileup. While the signal is larger than a given threshold, the peak counter counts the number peak in one pulse by using a logic pulse from a differentiator. The pileup is detected, if the number peak in one pulse is larger than one. To analyze accurately pulse height, a digital trapezoidal shaping filter is employed. Then the pulse height analyzer block detects peak of pulse and estimates baseline to calculate pulse height precisely. The code of peak is recorded in a 16384-word memory; the interface allows the PC independently to access data in memory through a USB port to display spectrum on PC.

## **III. RESULT AND DISCUSSION**

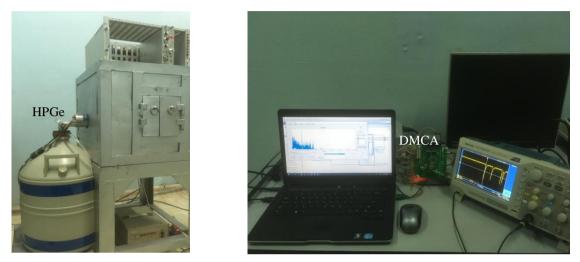

Several benchmark tests with an HPGe detector GC1518 model of Canberra, and gammaray calibration sources were carried out. The experiment setup configuration is presented in Figure 2. The HPGe detector is applied at a high voltage of 2,5KV. The signal from the preamplifier output is applied directly to the DMCA and the DMCA is connected to the PC by USB cable. The DMCA uses a power supply of 5V and it has a low power consumption of 0,3W. The PC software is developed by using MATLAB to record data and display spectrum.

Fig.2. The experiment setup using HPGe detector of GC1518 model of Canberra.

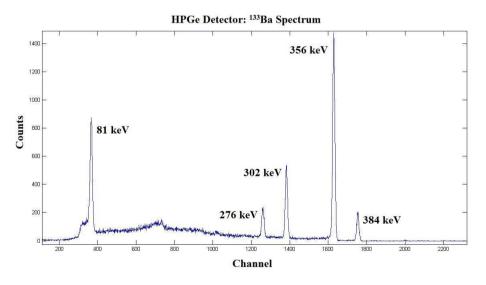

In fig. 3 shows the gamma spectra of <sup>133</sup>Ba radioisotope source collected by the DMCA. The low energy peaks of <sup>133</sup>Ba are completely separate.

Fig. 3.The  $\gamma$ -ray spectrum of <sup>133</sup>Ba radioisotope source.

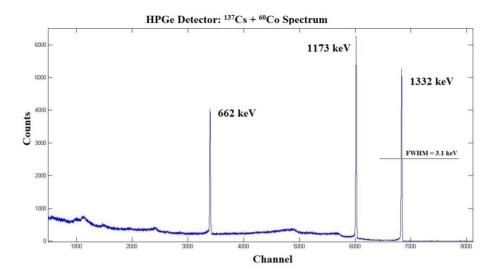

To examine the energy resolution of the DMCA, the peak of 1332 keV  $^{60}$ Co is used. Fig. 4 shows the gamma spectra of  $^{137}$ Cs and  $^{60}$ Co radioisotope sources, the energy resolution of the DMCA at 1332 keV  $^{60}$ Co is 3.1 keV.

**Fig.4.** The  $\gamma$ -ray spectrum of <sup>137</sup>Cs and <sup>60</sup>Co radioisotope sources.

## **IV. CONCLUSION**

This study reports a low-cost high-performance DMCA. The DMCA has a simple hardware, two main used IC, i.e. Artix-7 XC7A35T and AD6645. All pulse analysis algorithms are configured on FPGA. Hence, the DMCA performs in real time. The experiment results of throughput, energy resolution and quality of spectrum have shown that the performance of the proposed DMCA is remarkable.

### REFERENCES

- J.B. Simões, C.M. Correia, "Pulse processing architectures," Instruments and Methods in Physics Research A, vol. 422, no.1 pp. 405–410, 1999.

- [2] M. Bolic, V. Drndarevic," Digital gamma-ray spectroscopy based on FPGA technology," Nuclear Instruments and Methods in Physics Research A, vol. 482,no.3, pp. 761–766, 2002.

- [3] Z. Weihua,"The design of digital multi-channel analyzer based on FPGA," Energy Procedia, vol. 39, pp. 428-433, 2013.

- [4] P. S. Lee, C. S. Lee and J. H. Lee," Development of FPGA-based digital signal processing system for radiation spectroscopy," Radiation Measurements, vol. 48, pp. 12-17, 2013.

- [5] S. Korolczuk, S. Mianowski, J. Rzadkiewicz, P. Sibczynski, L. Swiderski, J. Szewinski and I. Zychor,"Digital approach to high rate Gamma-Ray spectrometry," in ANIMMA, 2015.

- [6] S. Saxena, and A. I. Hawari,"Investigation of FPGA Based Real Time Adaptive Digital Pulse Shaping for High Count Rate Applications," IEEE Transactions on Nuclear Science, vol. 64, no.7, pp. 1733 - 1738, 2017.

- [7] S. Darvish-Molla, K. Chin, W. V. Prestwich and S. H. Byun," Development of a compact and cost effective multi-input digital signal processing system," Nuclear Instruments and Methods in Physics Research A, vol. 879, pp. 13–18, 2018.

- [8] Z. J. Qin, C. Chen, J. S. Luo, X. H. Xie, L. Q. Ge and Q. F. Wu,"A pulse-shape discrimination method for improving Gamma-ray spectrometry based on a new digital shaping filter," Radiation Physics and Chemistry, vol. 145, pp. 193–201, 2018.

- [9] M. M. Ouda, M. S. El\_Tokhy, S. Hashima, I. I. Mahmoud, M. Amal-Eldin and N. I. Ziedan, "Hardware implementation for pileup correction algorithms in gamma ray spectroscopy," International Journal of Computer Applications, vol. 176, no. 6, pp. 43-48, 2017.

- [10] S. Kaur and S. P. Kaur, "Design of FIR filter using hanning window, hamming window and modified hamming window," in IJARCET, vol. 4, no.5, pp. 2440-2443, 2015.

- [11] P. C. Bhaskara and M. D. Uplaneb, "High Frequency Electromyogram Noise Removal from Electrocardiogram Using FIR Low Pass Filter Based On FPGA" Procedia Technology, vol. 25, pp. 497-504, 2016.

- [12] G. F. Knoll, "Radiation detection and measurement," 4th ed., John Wiley & Sons, Inc., 2010.

- [13] https://www.xilinx.com/products/silicon-devices/fpga/artix-7.html#documentation.

# THIẾT KẾ HỆ PHÂN TÍNH ĐA KÊNH KỸ THUẬT SỐ DÙNG FPGA CHO ĐẦU DÒ BÁN DẫN

# HOÀNG MINH VŨ, NGUYỄN VĂN KIÊN, PHẠM NGỌC SƠN, PHẠM HOÀI PHƯƠNG, NGUYỄN XUÂN TÂN

Viện Nghiên cứu hạt nhân, Đà Lạt, Việt Nam <u>hminhvu@gmail.com</u>

**Tóm tắt:** Nghiên cứu này trình bày thiết kế hệ phân tích biên độ đa kênh kỹ thuật số (DMCA) dùng mạch tích hợp mảng các phần tử logic lập trình được (FPGA) cho đầu dò bán dẫn. Phần cứng chính của hệ DMCA bao gồm một vi mạch tích hợp (IC) biến đổi tương tự sang số 16 bit (ADC) với tốc độ lấy mẫu 105 Mcps và FPGA Artix-7. Các thuật toán lọc hình thành xung, xác định đỉnh và hình thành phổ kỹ thuật số được thiết kế và mô phỏng trên phần mềm MATLAB. Các tài nguyên sử dụng của FPGA được tối ưu hóa trong quá trình thiết kế và mô phỏng, dẫn đến giảm chi phí cho phần cứng của DMCA. Tất cả các chức năng được cấu hình cứng trên FPGA, nên DMCA thực thi trong thời gian thực. Chồng chập xung và ổn định đường cơ bản (baseline) được xử lý để nâng cao độ phân giải năng lượng. Hệ DMCA đã được đo thử nghiệm với đầu dò bán dẫn của hãng Canberra (model: GC1518) dùng các nguồn chuẩn <sup>137</sup>Cs, <sup>60</sup>Co và <sup>133</sup>Ba. Độ phân giải năng lượng của hệ DMCA tại đỉnh 1332 keV của <sup>60</sup>Co đạt được 3,1 keV. Kết quả bước đầu cho thấy hệ DMCA có kích thước nhỏ, chi phí thấp và hoạt động ổn định, đáp ứng tốt cho mục đích nghiên cứu và đào tạo.

Từ khóa: DMCA, FPGA, đầu dò bán dẫn.